Recent Advances in Bipolar Electrostatic Chuck Design for 3nm Node Semiconductor Manufacturing

Recent Advances in Bipolar Electrostatic Chuck Design for 3nm Node Semiconductor Manufacturing - Advanced Beam Array Structures Enable Sub 3nm Node Wafer Handling

The push towards sub-3nm semiconductor manufacturing necessitates innovative approaches to wafer handling. Advanced beam array structures within bipolar electrostatic chucks (ESCs) are proving instrumental in this endeavor. These structures refine the configuration of the bipolar beams, resulting in a closer spacing of the electrodes. This optimization directly translates to more efficient wafer handling processes. Furthermore, the inherent flexibility of the beam structure allows for an adaptive gripping mechanism. This characteristic is particularly crucial for fragile, thin substrates, as it enables secure handling without the risk of surface damage or unwanted pressure. The challenges of processing and integrating the increasingly complex materials at the 3nm node are substantial. These advanced beam array structures are well-positioned to overcome these obstacles as leading semiconductor manufacturers like TSMC and Samsung continue to refine their 3nm technologies. The ability to confidently handle these delicate and intricate wafers will likely be a defining aspect of future semiconductor production advancements.

The development of increasingly sophisticated beam array structures is proving pivotal for wafer handling at the sub-3nm node. These arrays, intricately designed with micro-patterns, promise a more uniform distribution of electrostatic force across the wafer surface, a critical factor in minimizing defects during the manufacturing process. This finer control over the electric field not only improves thermal stability but also allows for the delicate handling of the extremely thin wafers used in these advanced nodes, mitigating the risk of damage during handling.

It seems intuitive that improved electrostatic force management should also lead to greater throughput, which appears to be the case. The precision afforded by these beam arrays results in more accurate wafer positioning and transfer compared to older chuck designs. Additionally, the use of advanced materials in these arrays can lead to reduced dielectric losses, which could improve the overall efficiency of the chuck during high-frequency operation.

Furthermore, the ability to integrate real-time sensing capabilities with these advanced beam arrays offers the potential for dynamic adjustment. This enables the chuck to automatically adapt to changing environmental conditions and process parameters, ensuring optimal wafer alignment throughout the manufacturing process. It's also notable that these newer designs often incorporate enhanced mechanical rigidity, allowing them to withstand the significant pressures encountered during automated wafer handling, a necessity considering the fragility of sub-3nm node structures.

Interestingly, modern fabrication techniques, like additive manufacturing, are playing a key role in producing these intricate beam array structures with very tight tolerances. This has opened up the possibility of customized beam array designs tailored to specific applications, which could potentially enhance performance. While offering many advantages, the advanced beam array systems are inherently more complex and can be expensive to implement. This cost factor could be a roadblock to wider industry adoption, making further research into optimizing the balance between performance and affordability critical moving forward. It will be interesting to see if the industry embraces these more complex solutions or if alternative approaches emerge to address the handling challenges at this crucial technology node.

Recent Advances in Bipolar Electrostatic Chuck Design for 3nm Node Semiconductor Manufacturing - Composite Laminated Plates Show Enhanced Chuck Performance at 3nm Scale

The emergence of composite laminated plates within bipolar electrostatic chuck (ESC) designs signifies a notable step forward in wafer handling, particularly at the demanding 3nm node in semiconductor manufacturing. These plates, structured with a compliant beam array, demonstrate improved clamping performance due to their enhanced mechanical flexibility. This flexibility allows for stronger attractive forces compared to traditional ESCs, a critical factor for managing the delicate wafers at this advanced node. Prior work highlighted the value of compliant beam structures, but the current approach emphasizes the optimization of multilayered composite designs, pushing the boundaries of electrostatic force control. While these composite laminates hold immense potential, the complexity introduced by their intricate fabrication necessitates careful consideration of cost implications to ensure widespread adoption. The success of these advanced materials and designs in improving wafer handling efficiency could redefine the landscape of semiconductor manufacturing at the forefront of technological development.

Bipolar electrostatic chucks (ESCs) are being explored for their potential in advanced semiconductor manufacturing, particularly at the challenging 3nm node. A key development in this area is the use of 3D-printed composite laminated plates in the compliant beam array structure of these chucks. These composite structures offer a way to potentially reduce the weight of the chuck, which is increasingly important in high-speed automated processes. The lighter weight could contribute to smoother and faster wafer handling, minimizing the risk of vibrations or instability during transfers.

It's also intriguing to consider how the material composition of these laminates can be fine-tuned to influence the chuck's thermal properties. Semiconductor manufacturing often involves extended periods of operation, generating heat. The use of specific materials within the composite structure could lead to more efficient heat dissipation, potentially improving the longevity and reliability of the chuck under intense operating conditions.

Moreover, the anisotropic nature of composite materials offers a degree of customization in the way electrostatic forces are distributed across the wafer surface. This capability could be critical for the 3nm node, where wafer fragility is a major concern. By precisely tailoring the force field, manufacturers might be able to minimize the risk of wafer damage during clamping and transfer.

Another benefit of composite laminates is the potential for enhanced mechanical resilience. Sub-3nm manufacturing is pushing the boundaries of material science and device design, with even minuscule surface imperfections potentially leading to device failures. The inherent robustness of some composites could address this challenge by offering a level of resistance against wear and tear.

Furthermore, composite materials can help address electromagnetic interference (EMI), which can be a major challenge in high-frequency semiconductor fabrication processes. The enhanced electrical insulation provided by certain laminates could potentially mitigate EMI and improve operational stability. It's noteworthy that these materials also might lead to better damping characteristics. Vibration reduction is crucial during wafer handling, as it can impact the precision of placement and overall yield.

Interestingly, some advanced composite materials exhibit self-healing properties. This unique characteristic could contribute to increased operational life in environments where equipment downtime is costly and disruptive.

Beyond material properties, the ability to integrate micropatterning within the composite laminate structure is also important. This capability could enable more precise shaping of the electrostatic field, offering better control over wafer positioning and handling.

While the benefits of composite laminated plates are compelling, their incorporation presents certain challenges. The manufacturing processes involved can be complex and potentially difficult to control. Maintaining consistent quality will be essential as semiconductor manufacturing continues its relentless push towards tighter tolerances and finer feature sizes at the 3nm node. The complex manufacturing techniques involved, therefore, could potentially impede wider industry adoption if reliability and production consistency cannot be readily addressed.

Recent Advances in Bipolar Electrostatic Chuck Design for 3nm Node Semiconductor Manufacturing - Elastically Deformable Components Address Non Flat Surface Challenges

The challenge of handling wafers with non-flat surfaces, particularly relevant in the demanding 3nm node of semiconductor manufacturing, is being addressed through the use of elastically deformable components within bipolar electrostatic chucks (ESCs). These flexible designs enable ESCs to more effectively clamp curved or non-planar dielectric materials. The key to this improved performance lies in the incorporation of compliant beam structures that can adapt to the surface contours of the wafer, reducing the risk of damage during handling. This adaptive capability is crucial as semiconductor manufacturing pushes into more complex geometries and thinner wafers.

Furthermore, the exploration of 3D-printed, layered structures within the ESC design introduces greater flexibility in accommodating a wider range of complex substrate shapes and sizes. This ability to handle varied geometries is vital in this era of increasingly intricate materials and device designs. While enhancing clamping and force distribution, the evolving ESC design also emphasizes the increasing intricacy and demanding nature of the 3nm manufacturing environment and beyond. The necessity to manage increasingly complex shapes effectively highlights the continuous evolution of semiconductor manufacturing and the need for adaptable tools to meet these challenges.

The use of elastically deformable components within bipolar electrostatic chucks (ESCs) offers a promising approach to addressing the challenges posed by non-flat wafer surfaces, especially at the demanding 3nm node. These deformable parts can adapt to the contours of the wafer surface, maintaining contact and preventing damage to the delicate structures typical of advanced semiconductor fabrication. This adaptability contributes to a more even distribution of electrostatic forces across the wafer, minimizing localized stress and the risk of surface defects during handling.

It's interesting to consider how the elastic properties of these components enhance the overall mechanical resilience of the chuck. The ability to deform helps absorb shocks and vibrations, potentially reducing wear and tear on the chuck itself, as well as minimizing the risk of damaging the wafers during transfer. Furthermore, the elastic nature allows for dynamic adjustments in response to changes in the wafer surface or thickness. This adaptive capability is particularly useful during manufacturing, where variations in wafer characteristics can arise due to differing process conditions.

It's also intriguing to consider the interplay between temperature and the stiffness of certain elastically deformable materials. This relationship offers the potential to fine-tune the electrostatic clamping force during various stages of semiconductor processing, ensuring reliable handling even under fluctuating thermal conditions. The integration of sensors and feedback systems with these elastically designed components could pave the way for more intelligent chucks. Such chucks could adapt automatically to changes in wafer properties during the manufacturing process, optimizing grip and ensuring stability throughout.

However, incorporating elastically deformable components introduces a layer of complexity into the ESC manufacturing process. Maintaining the desired material properties and geometries with precision is crucial for consistent performance. This need for precision might present scaling challenges as the industry looks to adopt these more advanced chuck designs on a larger scale. Ensuring efficient and consistent production at high volumes without compromising quality will be a crucial consideration for wider industry adoption.

The ongoing exploration of novel elastic materials, such as metamaterials, holds great potential for improving chuck designs even further. These advanced materials could lead to smarter chucks with finer control over electrostatic forces and ultimately contribute to improved operational efficiency in semiconductor handling environments. As the semiconductor industry continues its relentless pursuit of smaller feature sizes, the use of elastically deformable components in ESCs appears to offer a viable pathway for overcoming the challenges associated with wafer handling. However, continued research and development into manufacturing techniques and materials will be critical to realize the full potential of this promising technology.

Recent Advances in Bipolar Electrostatic Chuck Design for 3nm Node Semiconductor Manufacturing - SOI Wafer Processing Methods Improve Chuck Fabrication Precision

The increasing precision needed for 3nm node semiconductor manufacturing is driving innovations in bipolar electrostatic chuck (ESC) design. One key development involves the use of silicon-on-insulator (SOI) wafer processing techniques to enhance the precision of chuck fabrication. Using a 6-inch SOI wafer during the manufacturing process improves the uniformity of the etching process, making the chuck's components more consistent and reliable. Furthermore, the inherent layered structure of SOI wafers—consisting of silicon, silicon dioxide, and a handle layer—allows for a more accurate and controlled placement of the key electrical components within the ESC. This precision is crucial for safely handling the very thin and delicate wafers used in advanced semiconductor manufacturing.

However, the integration of SOI wafer processing methods into established chuck manufacturing processes is not without its difficulties. The complex manufacturing techniques and the need to maintain high levels of precision throughout the process can impact both manufacturing costs and consistency. This is a key challenge that needs to be overcome for the widespread adoption of this promising technology. The ability to precisely and reliably handle these ultra-thin wafers is becoming increasingly important as semiconductor manufacturing continues to push towards smaller and smaller feature sizes. Addressing these challenges related to SOI integration and maintaining quality could help make ESCs a more versatile and effective tool for semiconductor production at these advanced technology nodes.

Silicon-on-insulator (SOI) wafers are increasingly being used in the fabrication of bipolar electrostatic chucks (ESCs), particularly for the demanding 3nm node in semiconductor manufacturing. SOI's inherent advantages, like reduced parasitic capacitance and crosstalk, lead to improved electrical performance, which is critical for maintaining the precision required for handling fragile wafers at these scales. The better electrical control can lead to more refined management of electrostatic forces during wafer handling.

One aspect that researchers are interested in is SOI's potential for reducing thermal drift during the manufacturing process. Maintaining stable temperatures is crucial at the advanced nodes to avoid wafer deformation. The SOI manufacturing methods, involving techniques like laser processing and ion implantation, contribute to exceptional flatness and uniformity. This is beneficial for bipolar ESC designs, allowing for optimal clamping performance at the sub-3nm scale.

The layered structure of SOI wafers is also beneficial. It enhances the mechanical reliability compared to traditional silicon wafers, offering a degree of resilience that is important for handling the increasingly fragile and thin wafers being used. This resilience translates to a reduced risk of wafer damage or breakage, a serious concern at the 3nm node.

The ability to integrate SOI wafers with other novel materials, like graphene, is intriguing. The combination could significantly boost electrical performance and potentially enhance the mechanical characteristics of ESCs. Researchers are exploring these combinations for various, potentially very demanding, semiconductor applications.

SOI also opens up possibilities for aggressive wafer thinning without compromising structural integrity. This capability is vital as semiconductor manufacturers seek to create increasingly complex stacked device architectures and larger wafers with more layers. However, it's important to be aware of the cost and complexity introduced by using SOI materials.

Another noteworthy benefit is the possibility of reduced dielectric losses during ESC operation. This translates into higher efficiency for the wafer handling process and can be especially important in high-frequency applications. There is ongoing research into the efficiency gains offered by SOI.

Furthermore, SOI technology often utilizes microfabrication techniques that are essential for achieving the precise control needed to create electrostatic chucks capable of meeting the rigorous requirements of the nanometer scale. The complexity of 3nm node chip designs demands sophisticated interconnect structures, and the uniform electrical characteristics of SOI wafers can be advantageous for improving overall circuit performance.

In summary, SOI wafers show promise as a key element in ESC design for the 3nm node and beyond. While the benefits are substantial, challenges remain in manufacturing and cost optimization. As research progresses, it will be fascinating to observe whether the combination of SOI and sophisticated ESC designs contributes to improved yield and faster production for the increasingly intricate chips needed in future semiconductor technology.

Recent Advances in Bipolar Electrostatic Chuck Design for 3nm Node Semiconductor Manufacturing - Surface Smoothness Requirements Meet 3nm Node Manufacturing Standards

At the 3nm node, the demands for surface smoothness in semiconductor manufacturing have become paramount. The transition to this advanced node presents a significant hurdle, as wafer handling and processing must be executed with extreme care and precision. As leading companies such as TSMC and Samsung introduce innovative chip designs with new architectures, ensuring ultra-smooth surfaces on wafers becomes critical for ensuring device performance and reliability. The development of sophisticated bipolar electrostatic chuck designs with improved force application and stability is crucial to achieving the necessary surface smoothness. The 3nm node presents substantial challenges related to managing the intricacies of new materials while adhering to strict fabrication standards. Successfully navigating these challenges will require a deep understanding of surface interactions and an unwavering focus on process control. Ultimately, fulfilling the surface smoothness requirements will be a key element of successfully scaling manufacturing at the 3nm node.

The transition to 3nm node manufacturing necessitates an unprecedented level of surface smoothness, demanding tolerances nearly ten times stricter than those employed at the 5nm node. This often translates to a target surface roughness of under 0.5 nanometers—a significant challenge for existing fabrication techniques. While techniques like atomic layer deposition (ALD) offer a potential solution with their capability to create exceptionally thin coatings, achieving the desired smoothness requires incredibly precise control over deposition rates. Any inconsistencies can lead to critical failures in devices operating at this scale.

It's not just about geometry; the extreme miniaturization at the 3nm level makes devices acutely sensitive to electromagnetic fields. These fields can be influenced by even slight surface imperfections, often requiring tolerances as minuscule as 0.1% of the feature size. This sensitivity underlines the importance of achieving a truly pristine surface. Research suggests that surface smoothness can even affect the thermal behavior of materials used in the manufacturing process. Even minor surface roughness can disrupt the flow of heat, potentially impacting device performance and overall process efficiency.

Interestingly, nanoscale surface treatments such as plasma treatments and advanced polishing techniques have gained attention for their ability to produce exceptionally smooth surfaces. These treatments can enhance the electrostatic clamping force in the chuck without compromising the structural integrity of the wafer. This becomes increasingly vital as wafers become thinner and more delicate at the 3nm node.

To ensure that surfaces meet the rigorous demands of 3nm manufacturing, advanced characterization techniques like atomic force microscopy (AFM) are now essential. AFM can probe surface features at a resolution down to a few picometers, providing extremely detailed information and enabling rapid feedback during the design process. This allows engineers to refine designs quickly and iterate towards a final, optimized solution.

Emerging materials like hexagonal boron nitride (hBN) are currently being explored for their potential to combine outstanding surface smoothness with exceptional thermal conductivity. This combination could significantly benefit high-frequency applications where heat management is critical. However, the integration of new materials like this into established manufacturing processes always poses a challenge.

The impact of surface imperfections extends beyond just electromagnetic effects. Even minor deviations from the desired smoothness can lead to localized electric field distortions. These distortions can cause uneven wafer handling and contribute to an increase in defect rates. As the semiconductor industry relentlessly pushes toward even smaller scales, this concern only grows in significance.

Furthermore, maintaining optimal surface smoothness in bipolar electrostatic chucks is further complicated by environmental factors. Humidity and particulate contamination can readily disrupt the manufacturing process and introduce inconsistencies that challenge the current robustness of manufacturing methods. These challenges highlight the need for continued development of more resilient manufacturing processes.

Exciting new fabrication methods like holographic lithography hold promise for the future. They offer exceptionally fine control over material deposition at the synchrotron scale. If successfully implemented, holographic lithography could potentially revolutionize the standards for surface smoothness across the semiconductor industry. While challenging, it’s this drive for enhanced precision and reliability that will likely shape the future of 3nm and beyond semiconductor manufacturing.

Recent Advances in Bipolar Electrostatic Chuck Design for 3nm Node Semiconductor Manufacturing - Uniform Force Distribution Achieved Through Multi Beam Assembly Design

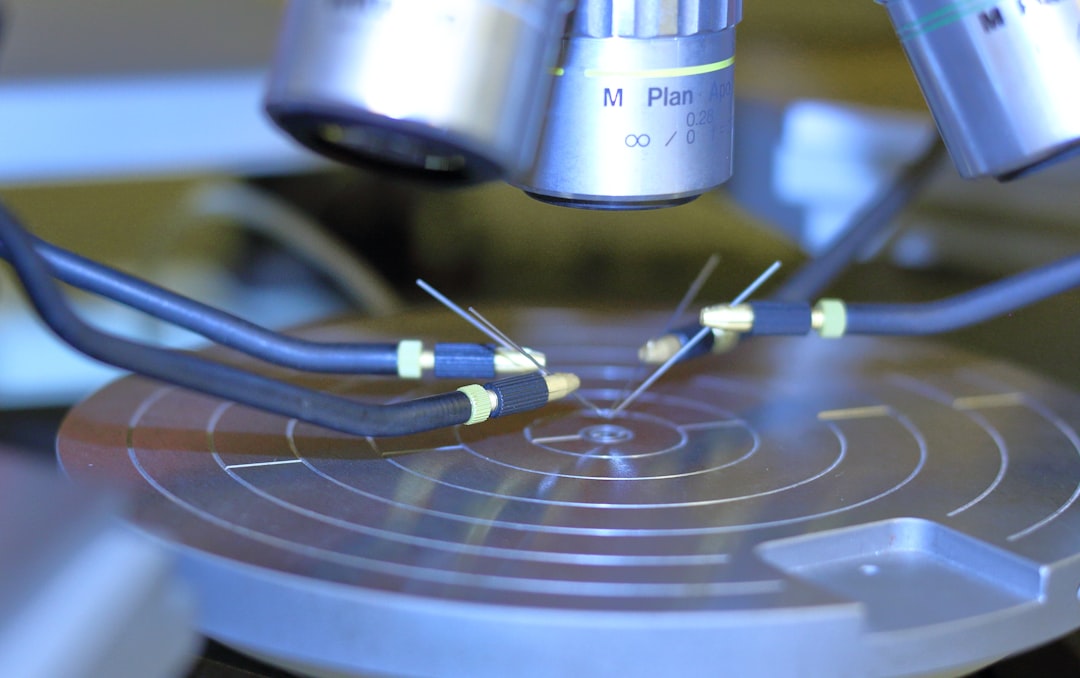

The pursuit of uniform force distribution in bipolar electrostatic chucks (ESCs) has led to the development of multi-beam assembly designs, a significant advancement particularly crucial for the complexities of 3nm semiconductor manufacturing. These designs incorporate flexible beam structures, enhancing the ability to adapt to wafer surfaces and providing more refined control over electrostatic forces. This results in a more consistent clamping force, which is vital for handling the fragile wafers used at this advanced node. The use of novel fabrication methods, such as abrasive water jet technology and the integration of flexible materials, has been instrumental in achieving the precise design and functionality of these multi-beam assemblies. This innovation not only minimizes the risk of wafer damage during handling but also underscores a critical step toward meeting the strict requirements of current semiconductor manufacturing processes. It remains to be seen, however, if the cost and complexity of implementing these multi-beam designs will hinder their wider adoption across the industry.

Bipolar electrostatic chucks (ESCs) are increasingly relied upon for handling wafers, especially in the demanding 3nm node of semiconductor manufacturing. A key innovation in this area is the use of multi-beam assemblies. These assemblies offer a path to overcome some limitations of older, planar designs by producing a more uniform distribution of electrostatic force. This more even distribution of force helps reduce wafer distortion during the clamping process, which can be particularly problematic with the thin and delicate wafers used at this node.

Further, the multi-beam approach allows for more dynamic adjustment. It's possible to integrate sensors into the chuck design, which could then be used to fine-tune the electric field in real-time. This flexibility could potentially compensate for temperature changes or variations in wafer thickness, making the clamping process more robust and adaptive. However, achieving this level of precision presents its own challenges. The manufacturing tolerances need to be incredibly tight – often on the order of a few micrometers—to ensure consistent performance.

Furthermore, researchers are actively exploring how to engineer the beam materials for optimized interactions with the wafer surface. This is critical as we use increasingly complex and diverse materials at the 3nm node. It's not just about mechanical interactions; the thermal and electrical characteristics of these new materials play a key role.

Interestingly, this multi-beam approach appears to lead to greater structural rigidity within the chuck itself. This characteristic might seem counterintuitive given that prior designs sometimes leveraged more flexible components. However, the increased rigidity of these assemblies helps ensure that the chuck retains its shape even under the stresses of high-speed automated handling, which is particularly crucial to preventing damage or defects.

The ability to customize the design of the beams—potentially by altering their shapes or materials—provides further benefits. This tailoring of beam properties to specific wafer types and handling processes can be a path to optimize the performance of the chuck for particular applications. The multi-beam approach also appears to minimize dielectric losses. The reduction in losses can improve overall efficiency and possibly help with thermal management in these high-frequency manufacturing environments.

This advanced approach, however, introduces complexities into the manufacturing process itself. Creating the multi-beam assemblies with uniform quality and precision across many beams within a single structure requires sophisticated manufacturing processes. It's a potential barrier to wider adoption if the production techniques and equipment necessary to ensure consistent quality aren't readily available. This complex fabrication could impact costs and limit the feasibility of the multi-beam approach for some applications.

It will be interesting to see if multi-beam approaches gain traction within the semiconductor manufacturing landscape. The ability to tailor designs, manage complex material interactions, improve rigidity, and potentially increase efficiency suggests that it could prove to be a useful tool in the toolbox as the industry continues to drive toward smaller and smaller features. The inherent challenges related to fabricating these structures with high consistency may necessitate a trade-off between the desired performance gains and cost-effectiveness.

More Posts from patentreviewpro.com:

- →New Patent Filing Reveals Advancements in Underwater RC Fish Technology for Marine Research

- →Recent Patent Analysis Single-Pull Tarp Tensioning System Introduces Novel Pulley Configuration for Enhanced Weather Resistance

- →Patent Analysis How Walters Gardens' 1998 Hosta 'Lakeside Zinger' Innovation Changed Miniature Garden Design

- →Understanding Hash Mismatches in Firmware Updates Causes and Solutions for Samsung Devices

- →Patent Analysis Innovations in Pella's Multi-Point Door Locking Systems

- →New Patent Filing Reveals Advancements in Motorized Beach Wagon Technology for 2025